8 Bit Serial To Parallel Converter Verilog Code

There is no pin for synchronization. The RS-232 serial protocol has a start and stop bit, logic 0 and 1 respectively. An idle channel will have a logic 1. So if the channel goes from idle to active, 0 will be the first thing you see. If you pick up the channel in the middle of transmission you'll end up having to find the pattern of 10 repeating every 10 bits (8-bit data). I actually don't think anyone does that type of synchronization.

From observation of devices that used RS-232 to receive data, I always remember seeing garbage if you hooked it up in the middle of a burst of data. I think most devices need a pause before achieving synchornization. Simatic s7 200s7 300mmcpasswordunlock20060911 rar file size.

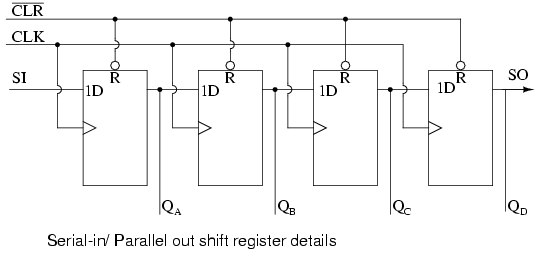

VHDL nbit - 8 bit serial to parallel shift register code test in circuit and test bench ISE Xilinx This video is part of a series which final design is a Controlled Datapath using a structural approach. Jan 16, 2018 - Question: Serial to verilog parallel code converter [UPDATED] When I examined the code for the Here is the. 8 Bit Serial To Parallel Converter.